intel AM

## ALIGN: Analog Layout, Intelligently Generated from Netlists

ALIGN Team

Presented by

Sachin S. Sapatnekar, University of Minnesota

CHIPS Alliance Fall Workshop

Supported in part by the DARPA IDEA Program

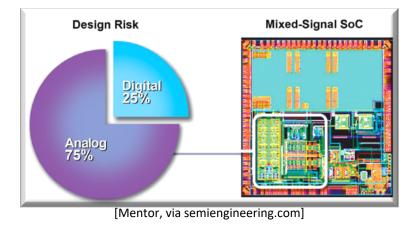

- "Analog everywhere" interaction with the real-world is all analog

- Analog design is a critical bottleneck for both design difficulty and respins

70% of re-spin issues are AMS in nature: How mixed-signal design can mess up a perfectly good SoC

[https://eda360insider.wordpress.com]

Rutenbar, ISPD 2010

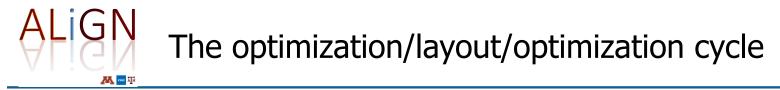

The optimization/layout/optimization cycle

Layout has significant impact on performance

٠

THE THE PARTY OF T Circuit-9 <u>uuun</u> Circuit-8 **Optimization** \_\_\_\_\_ Circuit-7 Circuit optimization THE OWNER Circuit-6 Max Error 11111 Circuit-5 Topology selection **Circuit Designer** Average Error anna Circuit-4 **Transistor sizing** Circuit-3 Circuit-2 Circuit-1 0.0 50.0 150.0 100.0 200.0 250.0 300.0 Error (%) **Layout Designer** Manual layout Manual layout **Cell generation Cell generation** Placement/routing Placement/routing [This takes weeks] [This takes weeks] time

3

Pre-Layout vs. Post-Layout Simulation Measurement

• Automatic layout helps the circuit designer

• FinFET design rules ("freedom from choice")

|  | Cell level |  | Block level |  |

|--|------------|--|-------------|--|

|--|------------|--|-------------|--|

- Complicated via rules, FinFET self-heating, ...

- Clearer expression of constraints

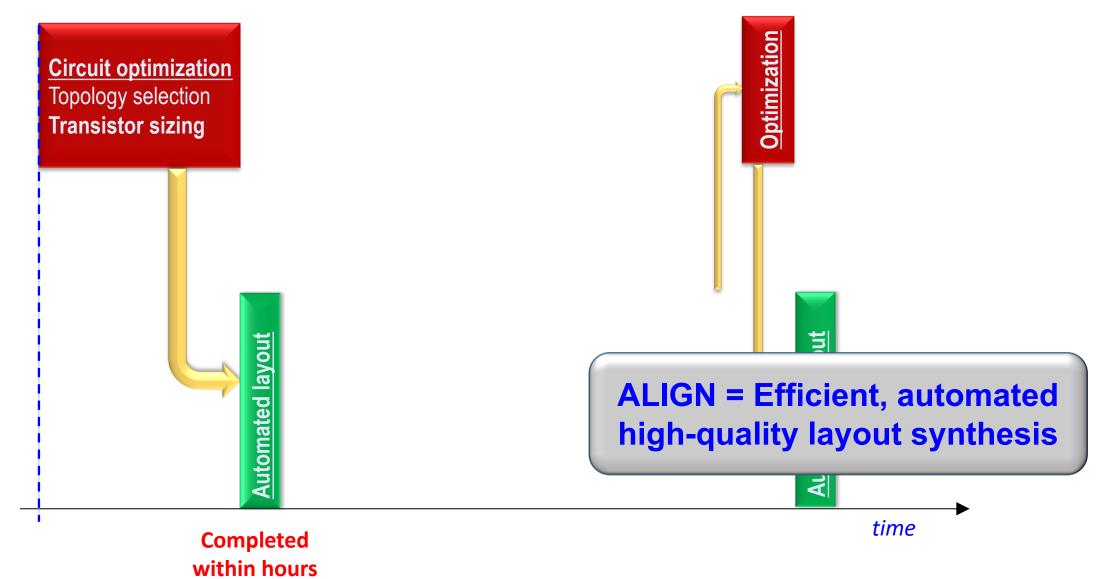

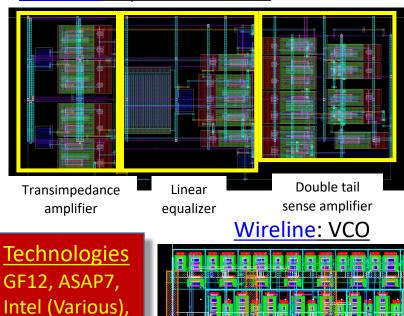

- Circuit classes: Low-frequency analog, Wireline, Wireless, Power delivery

• Machine learning advances

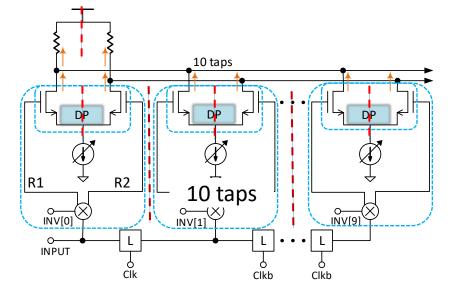

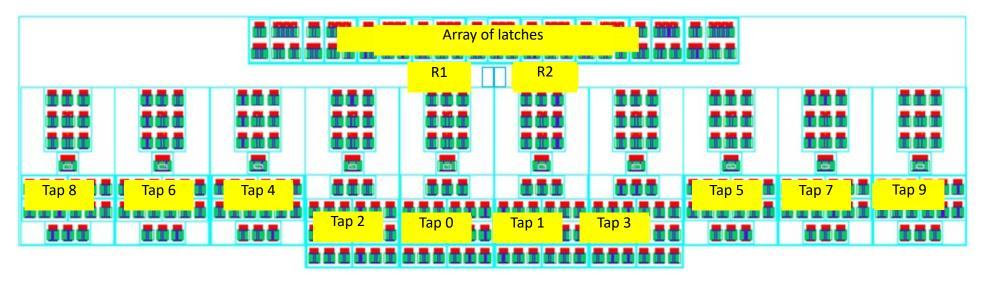

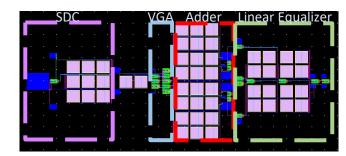

## **Example: 10-tap FIR Equalizer**

- Taps symmetric wrt each other; wrt R1 and R2

- Approximate matching: 5-bit/7-bit current sources

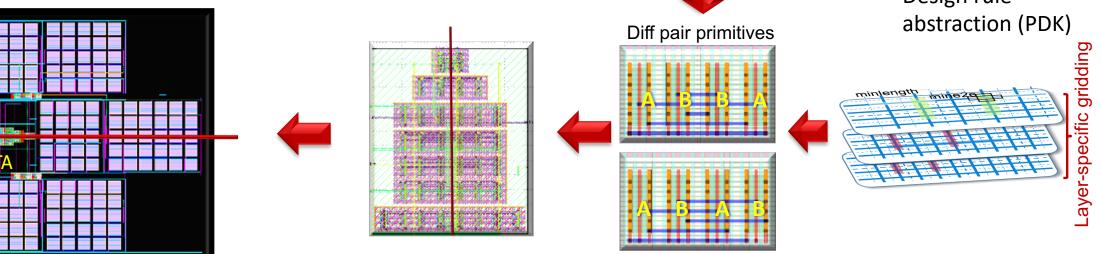

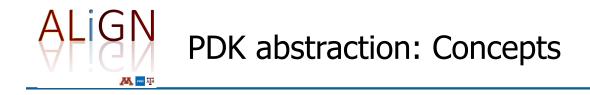

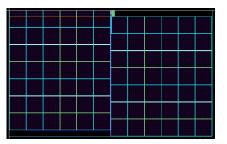

- Philosophy: Simplify design by restricting layout onto grids

- Distance-based design rules become enforced either:

- By adherence of objects to the grid, or

- By Boolean rules relating the presence/absence of objects on the grid

- Examples: Pitch, width and space, minimum end-to-end, via rules

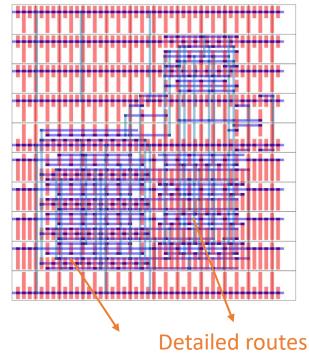

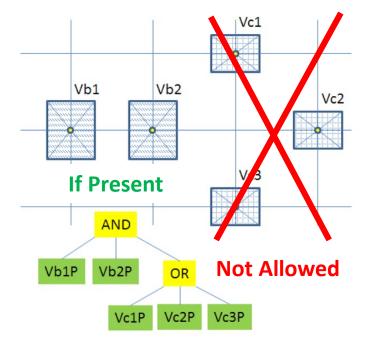

Via-to-via rule: diagonal vias disallowed

#

- Commercial PDKs (FinFET: 12nm, Bulk: 65nm), ASAP7, FinFET Mock PDK\*

- Internally within Intel to 22, 14, 10, and advanced FinFET process technologies

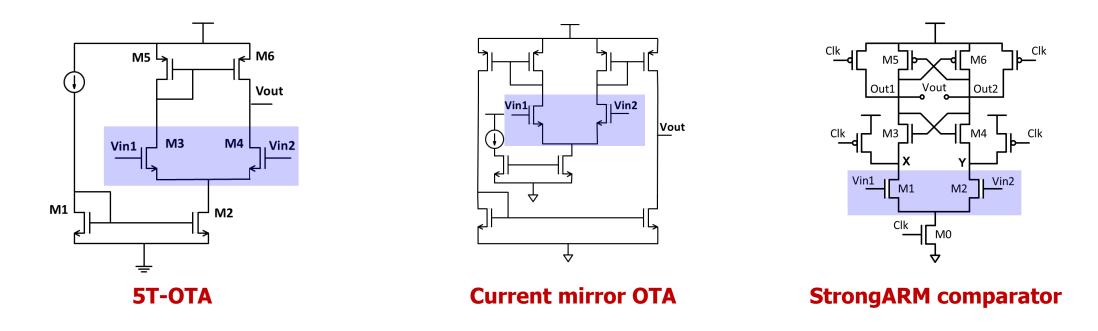

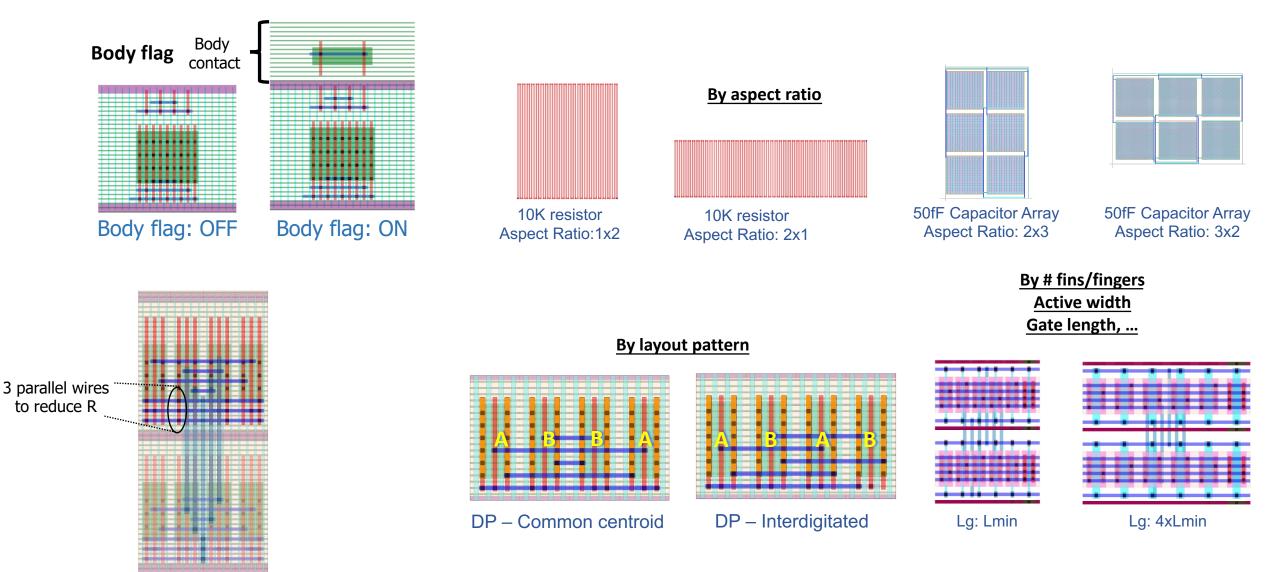

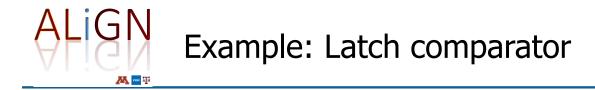

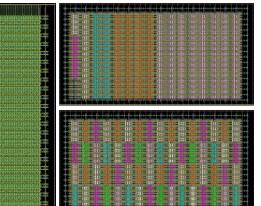

- Parameterized layout generation of a library of lowest-level primitive blocks

- Examples: current mirrors, differential pairs, Rs, Cs, ...

- Lowest level of hierarchy, assembled together through block assembly

Also: by # stacked transistors, by wire width within primitive, ...

## List of primitives

| Primitive                        | Schematic | Layout | Primitive                          | Schematic | Layout |

|----------------------------------|-----------|--------|------------------------------------|-----------|--------|

| Switch                           |           |        | Differential<br>load (CMC)         |           |        |

| Diode-connected<br>load<br>(DCL) |           |        | Current mirror<br>load (CMC_S)     |           |        |

| Differential pair<br>(DP)        |           |        | Cascode pair<br>(CP)               |           |        |

| Cross-coupled pair (CCP_S)       |           |        | Level shifter<br>(LS)              |           |        |

| Cross-coupled<br>pair1 (CCP)     |           |        | Dummy                              |           |        |

| Current mirror<br>(CM)           |           |        | Dummy1                             |           |        |

| Current mirror1<br>(CMFB)        |           |        | Decoupling<br>cap ( <u>decap</u> ) | -1        |        |

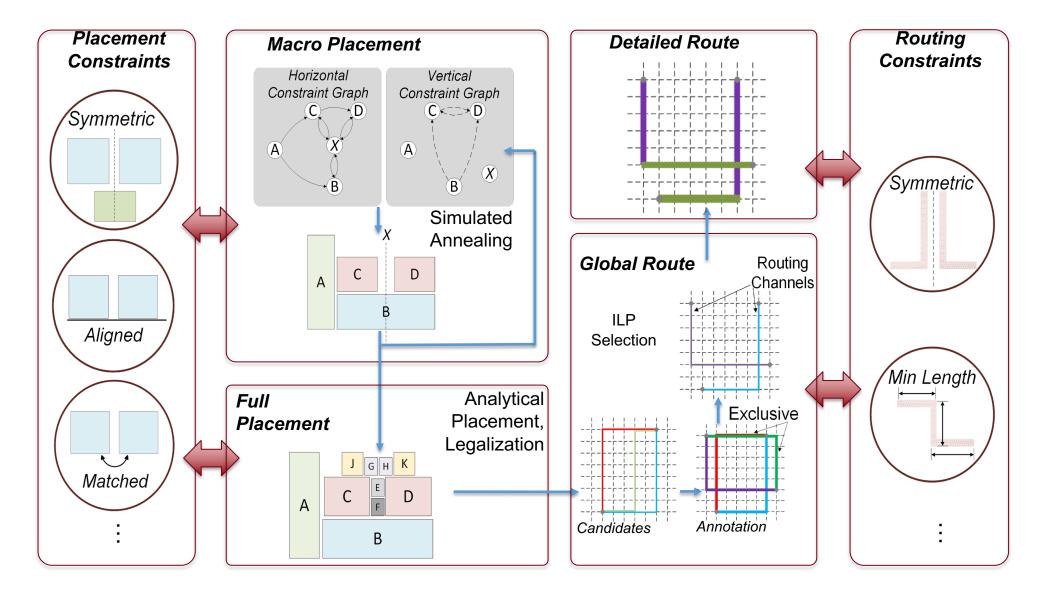

## Place-and-route framework

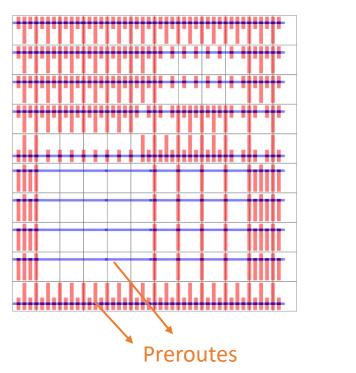

- SAT-based, design rule clean detailed router

- Allows modeling complex design rules (multiple patterning)

- Allows non-uniform metal grids

- Very effective for compact layout

### A Hypothetical Design Rule Violation [Suto, Intel]

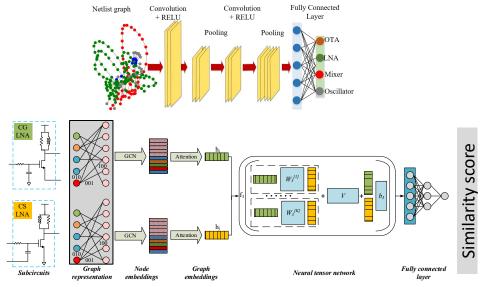

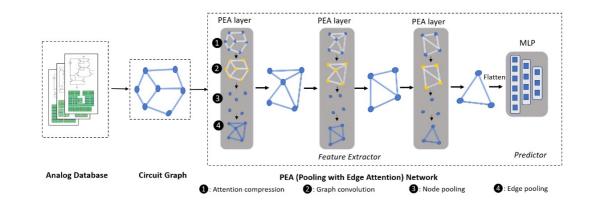

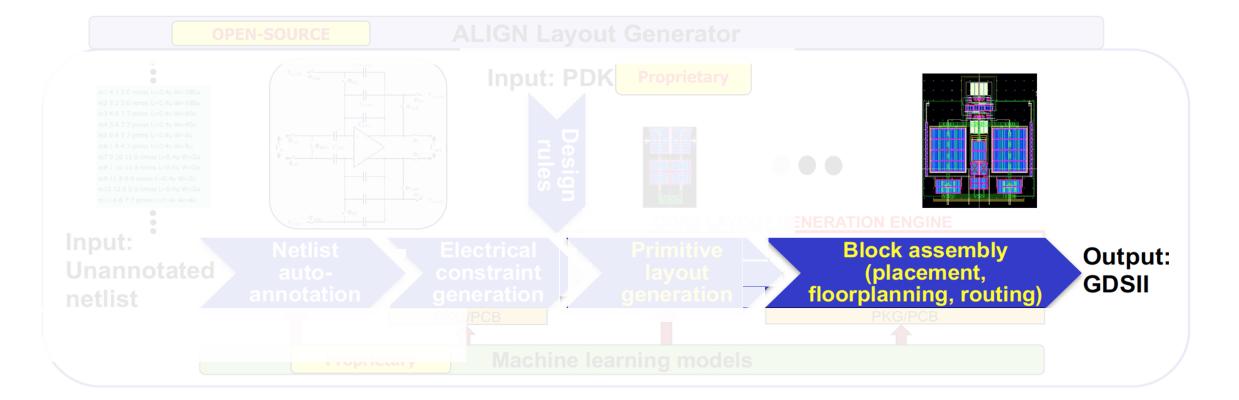

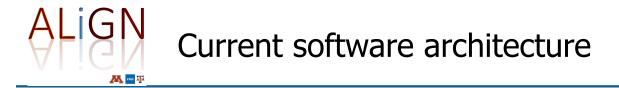

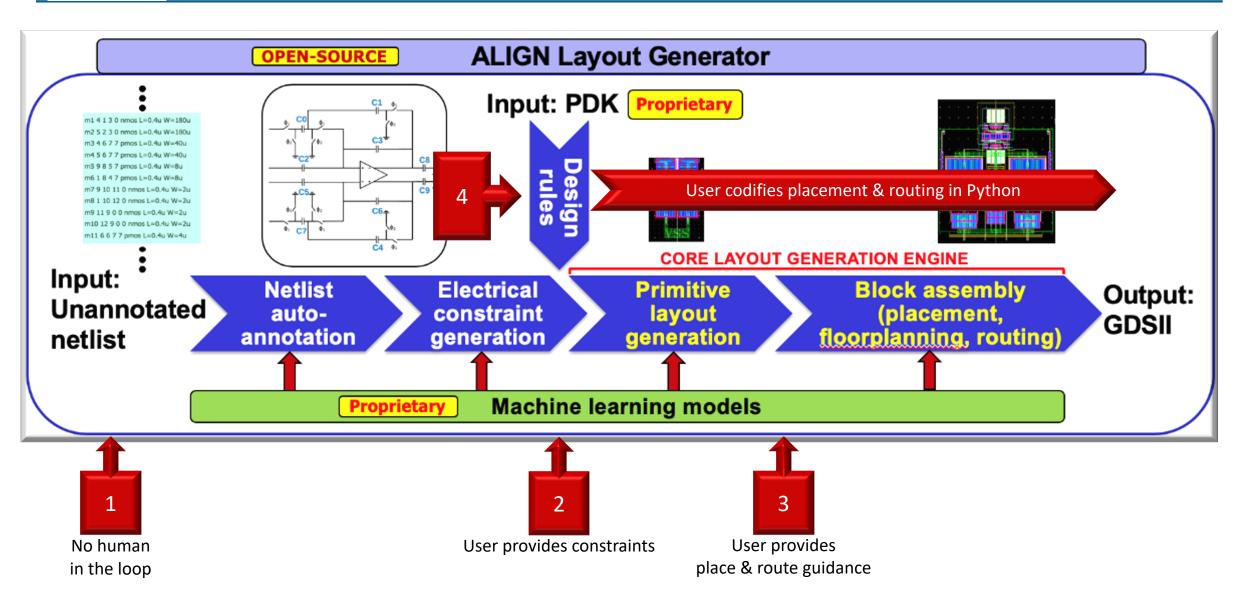

- The flow is divided into multiple stages: Topology identification, primitive generation, P&R, etc.

- Each stage was originally developed, more or less, at one site

- Sites had their own development environments, and wrote code in either C++ (TAMU) or Python (UMN, Intel)

- The team chose a decoupled architecture where interfaces between modules were done using files: either industry standard formats (likely simplified versions) or custom JSON schemas.

- Relied on Docker containers for quickly bringing up individual build environments

Highly Configurable: Each sub-package above can be used independently to create alternate entry points

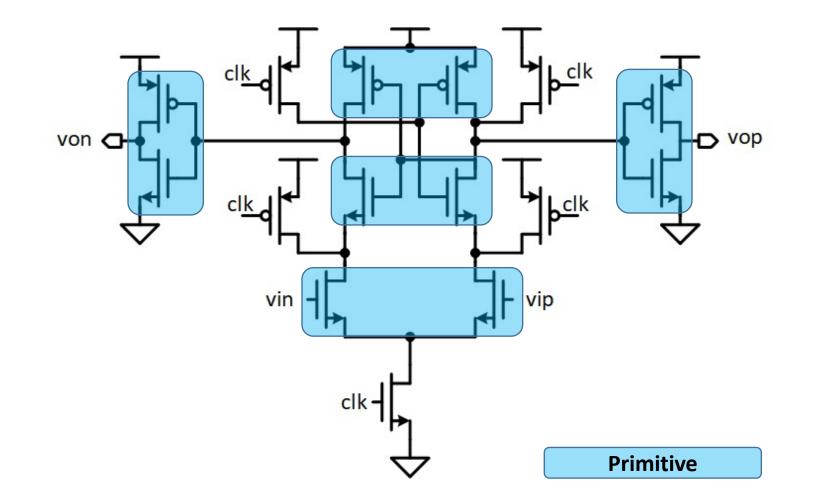

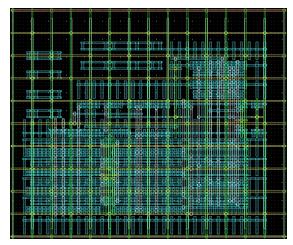

## Demo: Latch comparator on mock FinFET technology

Fundamental Research

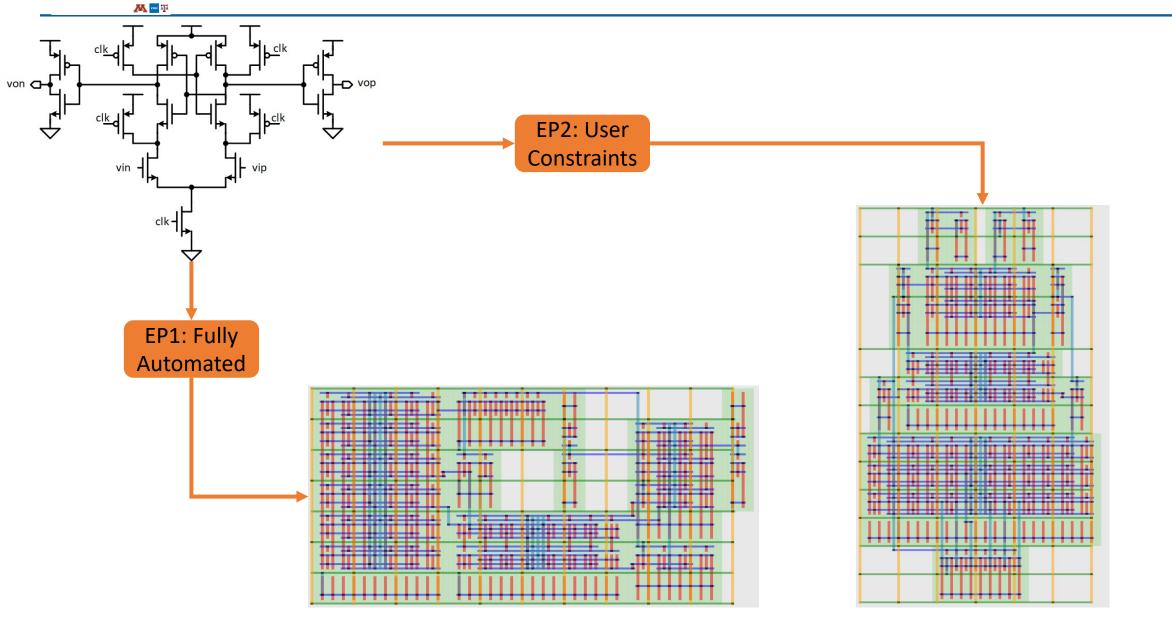

### Manual and generated layouts for comparator

Time cost comparison

Input referred offset voltage and comparison delay measured from 60 samples

Input Referred Offset Voltage (mV) 더 & 슈 뉴 ··

1

|    | LIGN-analoglayout / ALIGN        | I-public (Public)                                           | ⊙ Unwatch → 1          | 18 🌟 Unstar 87 💱 Fork 23                        |  |  |

|----|----------------------------------|-------------------------------------------------------------|------------------------|-------------------------------------------------|--|--|

| <> | Code 💿 Issues 85 🕅 Pu            | ull requests 29 💿 Actions 🛄 Projects 🕮 Wiki                 | 🛈 Security 🛛 🗠 Ir      | nsights                                         |  |  |

| ູນ | master - 우 91 branches 🛇         | 3 tags Go to file Add                                       | l file - Code -        | About                                           |  |  |

| ۲  | Lastdayends Merge pull request # | 809 from ALIGN-analoglayout/ 💷 🗸 18e5804 13 days ago        | • <b>4,978</b> commits | No description, website, or topics provided.    |  |  |

|    | .circleci                        | remove higigh_speed_comparator test                         | last month             | 🛱 Readme                                        |  |  |

|    | CircuitsDatabase                 | [.gitignore] Single source .gitignore                       | 8 months ago           | ৰ্বায় BSD-3-Clause License                     |  |  |

|    | Cktgen                           | [.gitignore] Single source .gitignore                       | 8 months ago           |                                                 |  |  |

|    | DetailedRouter                   | [.gitignore] Single source .gitignore                       | 8 months ago           | Releases 3                                      |  |  |

|    | PlaceRouteHierFlow               | fix typo                                                    | 13 days ago            | ALIGN release at end of Late<br>on Aug 24, 2020 |  |  |

|    | Viewer                           | addded unit tests                                           | 3 months ago           | + 2 releases                                    |  |  |

|    | align                            | correct comparator sizing (#800)                            | 15 days ago            |                                                 |  |  |

|    | bin                              | Update README.md for testcase; add missing script           | 5 months ago           | Packages                                        |  |  |

|    | dev                              | Merge pull request #798 from ALIGN-analoglayout/dependabot. | 29 days ago            | No packages published                           |  |  |

|    | docs                             | [constraint] Replace OrderBlocks with Order                 | 6 months ago           | Publish your first package                      |  |  |

|    | examples                         | correct comparator sizing (#800)                            | 15 days ago            |                                                 |  |  |

|    | pdks                             | rebasing master                                             | 2 months ago           | Used by 43                                      |  |  |

|    | regression_summaries             | Better column names                                         | 5 months ago           | <b>EEEEEEEEEEEEE</b>                            |  |  |

|    | tests                            | test for grid expansion                                     | 13 days ago            |                                                 |  |  |

| ß  | .codacy.yml                      | [codacy] Fix codacy yml path                                | 2 years ago            | Contributors 18                                 |  |  |

| ß  | .flake8                          | Revise align/pdk/finfet examples and refactor tests (#759)  | 3 months ago           | 😸 🚯 💮 🖨 🔂                                       |  |  |

| ß  | .gitattributes                   | [gitattributes] Change comment                              | 2 years ago            | 👶 🏟 🏟 🏠 🕰                                       |  |  |

| ß  | .gitignore                       | fix ignore                                                  | 2 months ago           | + 7 contributors                                |  |  |

| ~  | <b>A</b>                         | · · · · · · · · · · · · · · · · · · ·                       | -                      | 17 Sonthibutors                                 |  |  |

## https://github.com/ALIGN-analoglayout/ALIGN-public

#### E README.md

#### PASSED () code quality ! License BSD 3-Clause docs passing

## ALIGN: Analog Layout, Intelligently Generated from Netlists

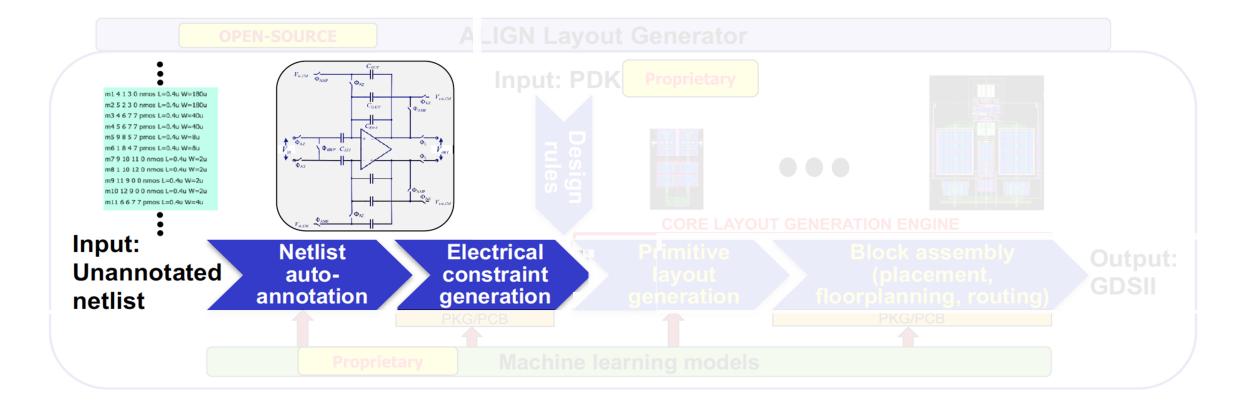

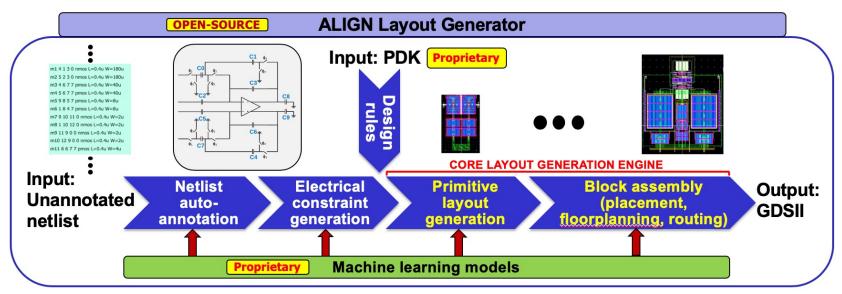

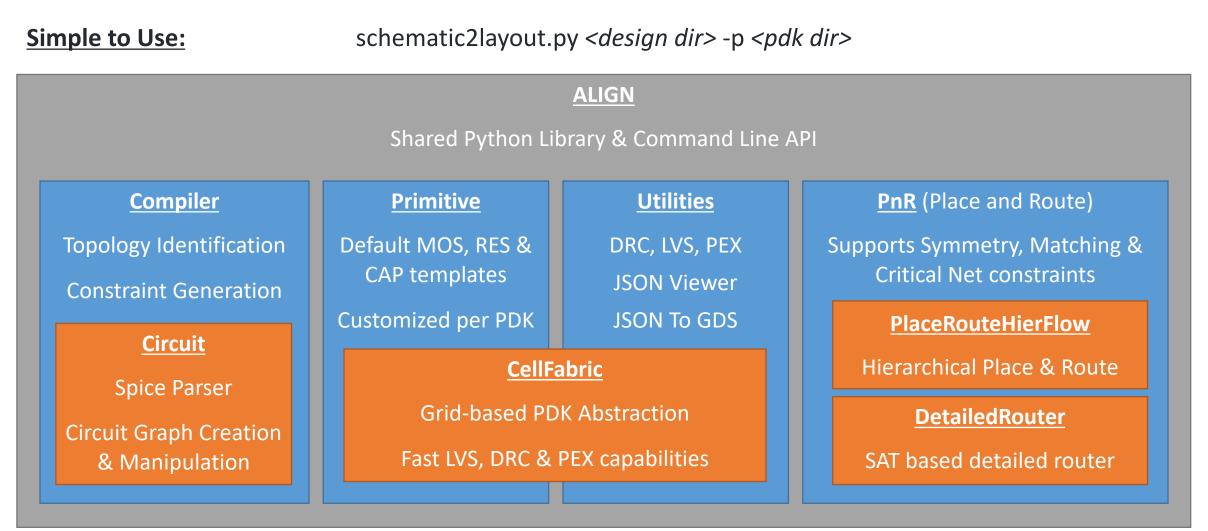

ALIGN is an open source automatic layout generator for analog circuits jointly developed under the DARPA IDEA program by the University of Minnesota, Texas A&M University, and Intel Corporation.

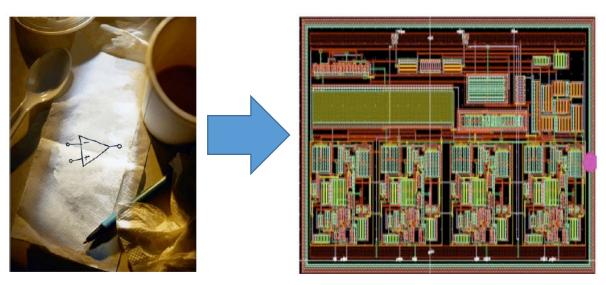

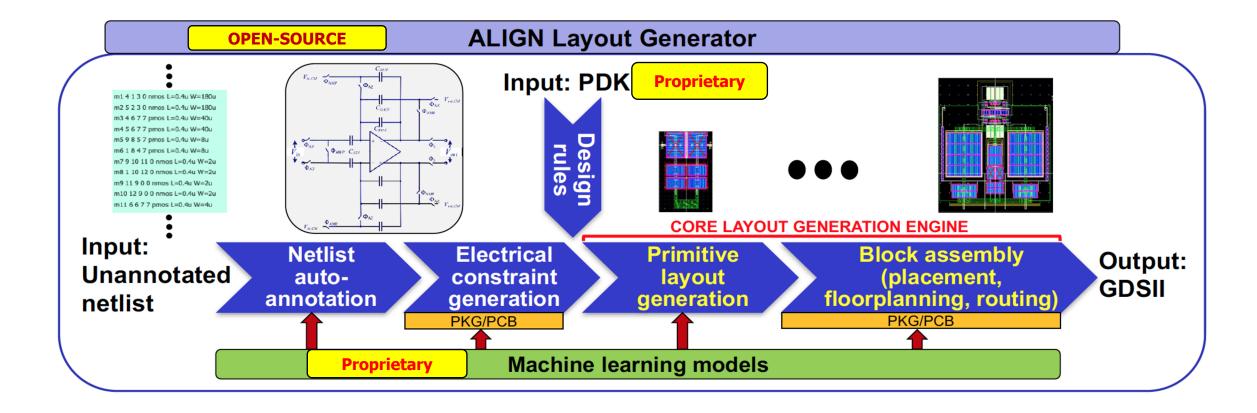

The goal of ALIGN (Analog Layout, Intelligently Generated from Netlists) is to automatically translate an unannotated (or partially annotated) SPICE netlist of an analog circuit to a GDSII layout. The repository also releases a set of analog circuit designs.

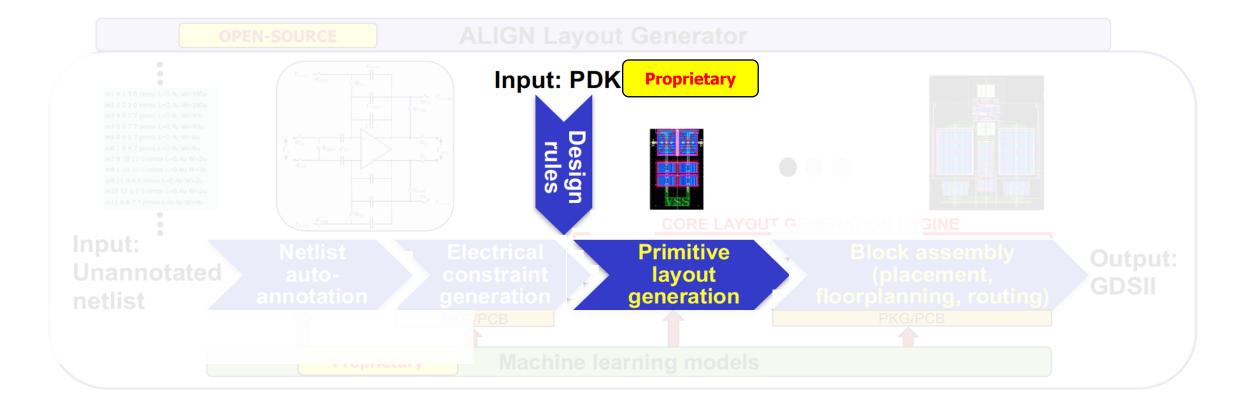

The ALIGN flow includes the following steps:

- Circuit annotation creates a multilevel hierarchical representation of the input netlist. This representation is used to implement the circuit layout in using a hierarchical manner.

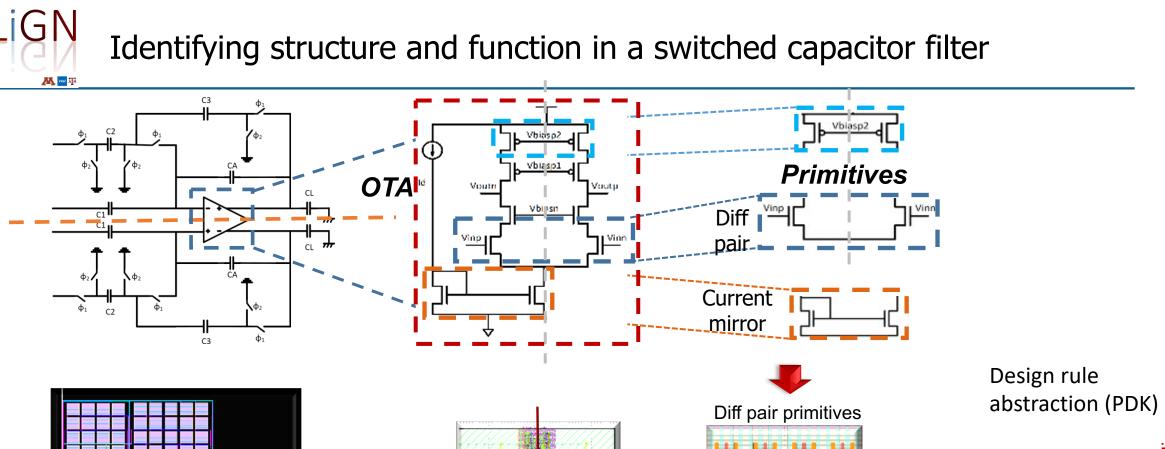

- Design rule abstraction creates a compact JSON-format representation of the design rules in a PDK. This repository provides a mock PDK based on a FinFET technology (where the parameters are based on published data). These design rules are used to guide the layout and ensure DRC-correctness.

- Primitive cell generation works with primitives, i.e., blocks at the lowest level of design hierarchy, and generates their layouts. Primitives typically contain a small number of transistor structures (each of which may be implemented using multiple fins and/or fingers). A parameterized instance of a primitive is automatically translated to a GDSII layout in this step.

- Placement and routing performs block assembly of the hierarchical blocks in the netlist and routes connections between these blocks, while obeying a set of analog layout constraints. At the end of this step, the translation of the input SPICE netlist to a GDSII layout is complete.

#### Inputs

- A SPICE netlist of the analog circuit

- Setup file

- Power and Gnd signals (First power signal is used for global power grid)

- Clk signal (optional)

- Digital blocks (optional)

- Library:(SPICE format)

- A basic built-in template library is provided, which is used to identify hierachies in the design.

More library elements can be added in the user\_template library.

- PDK: Abstracted design rules

- A mock FinFET 14nm PDK rules file is provided, which is used by the primitive cell generator and the place and route engine.

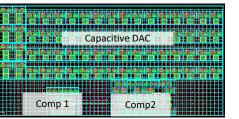

## Analog: Capacitive DAC

## Analog: Flash ADC

## Analog: SAR ADC

## Analog: SC Filter

TSMC65,

Sky130

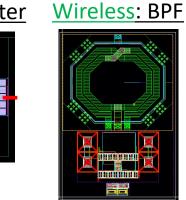

## Wireline: Optical Receiver

### Wireline: Equalizer

## Power delivery: SC DC-DC

## Power delivery: Powertrains

## Wireline: Comparator

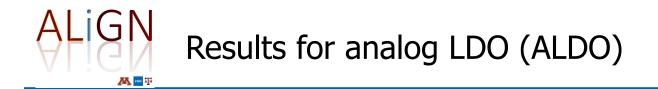

## Power delivery: LDO