## Practical Adoption of Open Source System Verilog Tools

**CHIPS Alliance Fall Workshop, 2021-10-12** Michael Gielda, mgielda@antmicro.com

Practical Adoption of Open Source System Verilog Tools

antmicro

## WHY DO WE NEED SYSTEMVERILOG SUPPORT IN OPEN SOURCE TOOLS?

- Proprietary licensing of existing tools makes it hard to build scalable, reproducible CIs

- Especially publicly accessible CIs in multi-org projects - OpenTitan, CHIPS Alliance

- Number of open source cores and lots of pre-existing IP implemented in SystemVerilog, e.g.

- SweRV

- <u>Ibex</u>

- BlackParrot

- <u>Core-V</u>

- Open source tools will help building a collaborative ecosystem around ASIC and FPGA design

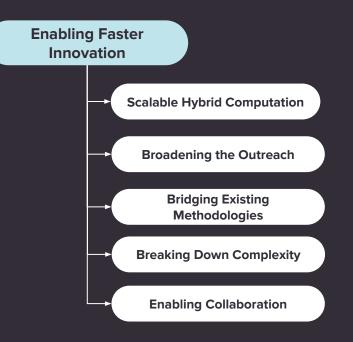

#### HOW TO BUILD AN OPEN SOURCE SYSTEMVERILOG ECOSYSTEM

- Identify missing functionalities and features

- Reuse existing solutions

- There are many existing projects which can be improved

- Create well documented and transparent projects

- Include automated tests and status reporting in projects

- Cooperate with others

- Gather information on what is needed

- Provide incremental value

#### **CHIPS ALLIANCE & HDLS**

- CHIPS wants to encourage all sorts of open source ASIC development - and acknowledges that the future ecosystem will be pluralistic

- workgroups for both Chisel and SystemVerilog peacefully coexist and collaborate within our Technical Steering Committee

- See <u>https://chipsalliance.org/workgroups/</u> for list of workgroups, <u>https://github.com/chipsalliance/tsc</u> for current TSC composition

#### SO, WHAT DO WE MEAN BY PRACTICAL ADOPTION?

#### LAY OF THE LAND: SV-TESTS

- Test suite to determine the SystemVerilog

support level in various open source tools

- Pinpoint all the supported/missing SV features

- Report: <u>symbiflow.github.io/sv-tests</u>

- Three types of tests:

- SystemVerilog features

- Existing third party test suites

- Selected open source IP cores (SweRV, Ibex etc.)

|                                                                                                                                                                                                                                              |                  |          |          |               |          |                                                                                                 |                                                                                                                                       |                                                                                           |                                   | Search:                                                             |                          |             |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|----------|---------------|----------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------|--------------------------|-------------|-----|

| 0                                                                                                                                                                                                                                            |                  | icarus 🗄 | moore 0  | moore_parse : | odin 0   | slang 0                                                                                         | surelog 0                                                                                                                             | sv2v_zachjs :                                                                             | sv_parser (                       | tree_sitter_verilog                                                 | verible 0                | verilator 0 | yos |

| Ariane RISC-V core                                                                                                                                                                                                                           | ariane           | 0/1      | 0/1      | 0/1           | 0/1      | 0/1                                                                                             | 0/1                                                                                                                                   | 0/1                                                                                       | 1/1                               | 8/1                                                                 | 0/1                      | 0/1         | 0.  |

| Tests imported from Basejump STL                                                                                                                                                                                                             | basejump         | 0/302    | 32/302   | 164/302       | 0/302    | 97/302                                                                                          | 289/302                                                                                                                               | 292/302                                                                                   | 296/302                           | 0/302                                                               | 299/302                  | 98/302      | 0/: |

| BlackParrot RISC-V core                                                                                                                                                                                                                      | black-<br>parrot | 874      | 8/4      | 8/4           | 8/4      | 8/4                                                                                             | 8/4                                                                                                                                   | 8/4                                                                                       | 4/4                               | 8/4                                                                 | 874                      | 8/4         | 8   |

|                                                                                                                                                                                                                                              | earlgrey         | 0/1      | 0/1      | 0/1           | 0/1      | 0/1                                                                                             | 0/1                                                                                                                                   | 0/1                                                                                       | 0/1                               | 0/1                                                                 | 0/1                      | 0/1         | 0   |

| FX68K m68k core                                                                                                                                                                                                                              | fx68k            | 0/1      | 0/1      | 1/1           | 0/1      | 1/1                                                                                             | 1/1                                                                                                                                   | 1/1                                                                                       | 1/1                               | 0/1                                                                 | 1/1                      | 1/1         | 0   |

| Tests imported from hdlConvertor                                                                                                                                                                                                             | hdiconv          | 0/386    | 78/306   | 127/386       | 8/306    | 69/386                                                                                          | 283/306                                                                                                                               | 87/306                                                                                    | 305/306                           | 191/306                                                             | 261/306                  | 67/306      | 44. |

| Ibex RISC-V core                                                                                                                                                                                                                             | ibex             | 0/1      | 0/1      | 0/1           | 0/1      | 0/1                                                                                             | 1/1                                                                                                                                   | 1/1                                                                                       | 1/1                               | 8/1                                                                 | 1/1                      | 1/1         | 0   |

| Tests imported from ivtest                                                                                                                                                                                                                   | ivtest           | 8/2173   | 451/1982 | 1474/1982     | 298/1982 | 1354/1902                                                                                       | 1868/2173                                                                                                                             | 1484/1982                                                                                 | 1899/1902                         | 34/1982                                                             | 1873/1982                | 1501/2173   | 450 |

| RSD RISC-V core                                                                                                                                                                                                                              | rsd              | 0/1      | 0/1      | 0/1           | 0/1      | 0/1                                                                                             | 0/1                                                                                                                                   | 0/1                                                                                       | 1/1                               | 8/1                                                                 | 0/1                      | 0/1         | 0   |

| Various sanity checks                                                                                                                                                                                                                        | sanity           | 1/1      | 1/1      | 1/1           | 1/1      | 1/1                                                                                             | 1/1                                                                                                                                   | 1/1                                                                                       | 1/1                               | 1/1                                                                 | 1/1                      | 1/1         | 1   |

| SCR1 RISC-V core                                                                                                                                                                                                                             | scr1             | 0/1      | 8/1      | 8/1           | 8/1      | 8/1                                                                                             | 1/1                                                                                                                                   | 1/1                                                                                       | 1/1                               | 8/1                                                                 | 8/1                      | 8/1         | e   |

| SweRV RISC-V core                                                                                                                                                                                                                            | swerv            | 8/1      | 8/1      | 8/1           | 8/1      | 0/1                                                                                             | 1/1                                                                                                                                   | 1/1                                                                                       | 0/1                               | 8/1                                                                 | 8/1                      | 1/1         | e   |

| Taiga RISC-V core                                                                                                                                                                                                                            | taiga            | 8/1      | 8/1      | 8/1           | 8/1      | 0/1                                                                                             | 1/1                                                                                                                                   | 8/1                                                                                       | 1/1                               | 8/1                                                                 | 1/1                      | 0/1         | e   |

| Tests imported from utd-SystemVerilog                                                                                                                                                                                                        | utd-sv           | 8/295    | 114/295  | 292/295       | 183/295  | 119/295                                                                                         | 294/295                                                                                                                               | 287/295                                                                                   | 260/295                           | 272/295                                                             | 294/295                  | 125/295     | 286 |

| Tests imported from UVM                                                                                                                                                                                                                      | uvm              | 0/1      | 0/1      | 0/1           | 0/1      | 0/1                                                                                             | 0/1                                                                                                                                   | 0/1                                                                                       | 1/1                               | 1/1                                                                 | 1/1                      | 0/1         | e   |

| Tests imported from Yosys                                                                                                                                                                                                                    | yosys            | 9/184    | 132/184  | 155/184       | 72/184   | 167/184                                                                                         | 184/184                                                                                                                               | 172/184                                                                                   | 183/184                           | 164/184                                                             | 176/184                  | 169/184     | 154 |

| White space                                                                                                                                                                                                                                  | 5.3              | 6/7      | 7/7      | 7/7           | 1/7      | 7/7                                                                                             | 7/7                                                                                                                                   | 7/7                                                                                       | 7/7                               | 8/1                                                                 | 1/1                      | 7/7         | 7   |

| Comments                                                                                                                                                                                                                                     | 5.4              | 6/7      | 7/7      | 7/7           | 0/7      | 7/7                                                                                             | 7/7                                                                                                                                   | 7/7                                                                                       | 7/7                               | 1/1                                                                 | 1/1                      | 7/7         | 7   |

| Identifiers, keywords, and system names                                                                                                                                                                                                      | 5.6              | 1/2      | 2/2      | 2/2           | 2/2      | 2/2                                                                                             | 2/2                                                                                                                                   | 2/2                                                                                       | 2/2                               | 2/2                                                                 | 2/2                      | 2/2         | 2   |

| Escaped identifiers                                                                                                                                                                                                                          | 5.6.1            | 0/2      | 2/2      | 2/2           | 1/2      | 2/2                                                                                             | 2/2                                                                                                                                   | 2/2                                                                                       | 2/2                               | 2/2                                                                 | 2/2                      | 2/2         | 2   |

| tting<br>crightin: full serv core test<br>f heave sources: 1)<br>bud fait: 0<br>criss: 0<br>criss: prove<br>dirs: //mpfs/src/github/sv-tests/third_party/co<br>medule: serv ranger<br>d: parting<br>sources/sources/serv/corfins/snassbots/d |                  |          |          |               |          | 1 // NOTE /<br>2 // This<br>3 //<br>4 // cmd:<br>5 //<br>6 define /<br>8 define /<br>9 define / | NOTE NOTE NOTE<br>s an automatic<br>swerv -snaps<br>N_INST_ACCESS<br>N_INST_ACCESS<br>N_INST_ACCESS<br>N_INST_ACCESS<br>N_INST_ACCESS | ally generated f:<br>hot=default -amb,<br>MASKS 'enffffff<br>DIABLE4 1'N0<br>DIABLE3 1'N0 | TE NOTE NOTE N<br>Lle by joseph.r | efines.vh<br>otë motë notë notë notë not<br>ahmeh on Tue Oct 15 13: | : NOTE<br>13:16 PDT 2019 |             |     |

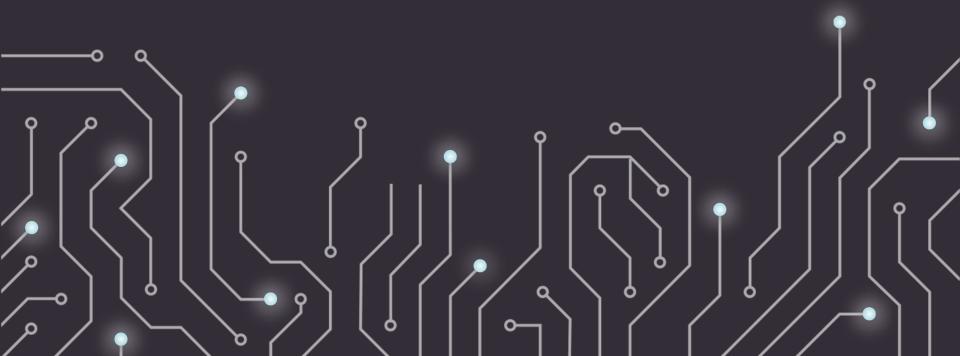

#### REUSE: SURELOG / UHDM

n-tests

- How to provide good SV support across the board?

- <u>Surelog</u>: open source SystemVerilog 2017

Pre-processor, Parser, Elaborator and UHDM

Compiler

- Universal Hardware Data Model (<u>UHDM</u>) is used to exchange the information about elaborated SV design between the parser and other tools

- Integrating UHDM into Verilator and Yosys

- Can <u>parse</u>, <u>synthesize</u> and <u>simulate</u> <u>OpenTitan's</u> <u>Ibex core</u> directly from source -<u>https://github.com/chipsalliance/UHDM-integratio</u>

# 🛟 opentitan

#### UHDM/SURELOG + VERILATOR/YOSYS

#### INCREMENTAL VALUE: VERIBLE

- Open source SV linter/formatter

- Released by Google on <u>GitHub</u>, onboarded into CHIPS

- Actively developed by Google and Antmicro

- Used e.g. in Ibex (OpenTitan) CI

- Very versatile, with lots of practical uses

```

1 // Copyright lowRISC contributors.

Files

2 // Copyright 2018 ETH Zurich and University of Bologna, see also CREDITS.md.

3 // Licensed under the Apache License, Version 2.0, see LICENSE for details.

::/

4 // SPDX-License-Identifier: Apache-2.0

rtl/

ibex alu.sv

`ifdef RISCV FORMAL

define RVFI

ibex compressed decoder

endif

ibex controller.sv

ibex core.sv

`include "prim_assert.sv"

ibex cs registers.sv

12

ibex decoder.sv

/**

* Top level module of the ibex RISC-V core

ibex ex block.sv

14

*/

ibex fetch fifo.sv

15

module ibex_core #(

ibex id stage.sv

16

parameter bit

PMPEnable

- 1'b0.

ibex if stage.sv

parameter int unsigned

PMPGranularity

= 0,

18

parameter int unsigned

- 4,

ibex load store unit.sv

19

parameter int unsigned

MHPMCounterNum

= 0.

ibex multdiv fast.sv

20

parameter int unsigned

MHPMCounterWidth = 40.

ibex multdiv slow.sv

21

parameter bit

RV32E

= 1'b0,

ibex pka.sv

22

parameter ibex pkg::rv32m e

RV32M

- ibex pkg::RV32MFast,

Definitions:

rtl/ibex core.sv

33: parameter int unsigned

DmHaltAddr

= 32'h1A110800.

References:

rtl/ibex core.sv

401: .DmHaltAddr

(DmHaltAddr

```

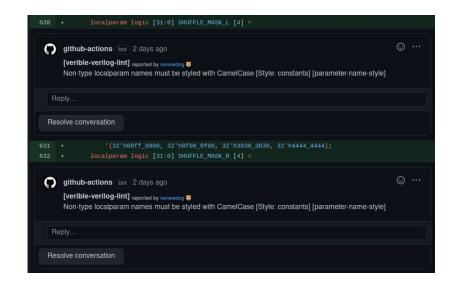

#### **VERIBLE - LINTING**

- Linter a static code analysis tool to spot and fix stylistic errors and bugs in SystemVerilog code

- Allows enforcement of rules on a project or company level in various SystemVerilog projects to follow authoritative style guides

- The rules vary from simple ones to more sophisticated and are highly configurable

- E.g. making sure the module name matches the file name, checking variable naming conventions

\$ verible-verilog-lint --ruleset all core.sv core.sv:3:11: Interface names must use lower\_snake\_case naming convention and end with \_if. [Style: interfaceconventions] [interface-name-style]

#### VERIBLE - FORMATTING

- Formatter a complementary tool for the linter used to automatically detect various formatting issues like improper indentation or alignment

- As opposed to the linter, it only detects and fixes issues that have no lexical impact on the source code

- Linter + formatter can effectively remove all the discussions about styling, preferences and conventions from all pull requests

- Developers can then focus solely on the technical aspects of the proposed changes

```

$ cat sample.sv

typedef struct {

bit first;

bit second;

bit

third

bit fourth;

bit fifth; bit sixth;

foo_t;

$ verible-verilog-format sample.sv

typedef struct {

bit first;

bit second;

bit third;

bit fourth;

bit fifth;

bit sixth;

} foo_t;

```

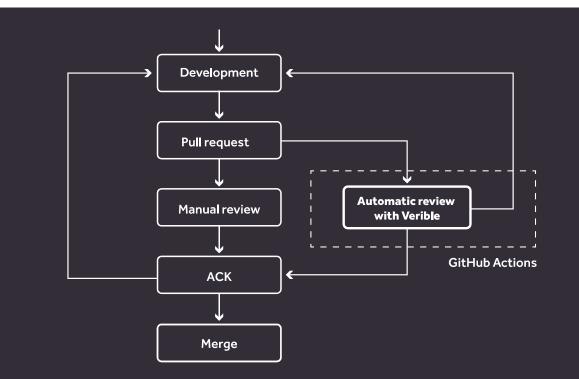

#### **VERIBLE GITHUB ACTIONS**

#### VERIBLE LINTER GITHUB ACTION

- chipsalliance/verible-linter-action

- Any GitHub-hosted open-source or private project can inform commiters about the issues detected in their code

- Wide range of applications can be devised, from faster pull requests reviews, to isolating erroneous portions of code

- Blog note

#### VERIBLE FORMATTER GITHUB ACTION

- <u>chipsalliance/verible-formatter-action</u>

- Same as above, except it automatically generates code suggestions which can just be accepted - instant benefit!

| <ul><li>● githu</li></ul> | ub-actions (bot) reviewed on Aug 31                             | Labels<br>None yet   | ٤                                                                         |         |

|---------------------------|-----------------------------------------------------------------|----------------------|---------------------------------------------------------------------------|---------|

| github-a                  | github-actions bot left a comment                               |                      |                                                                           | ε       |

|                           | ng comments which cannot be posted as a review comm             | nent to avoid GitHub | None yet                                                                  |         |

| Rate Lim                  |                                                                 |                      | Milestone                                                                 | ٤       |

|                           | verilog-format<br>compressed_decoder.sv[271]                    | No milestone         |                                                                           |         |

|                           | ompressed_decoder.sv[289]<br>ompressed_decoder.sv[299]          | Linked issues        | ٤                                                                         |         |

| _                         |                                                                 |                      | Successfully merging<br>may close these issue                             |         |

| rt                        | l/ibex_branch_predict.sv                                        | None yet             |                                                                           |         |

|                           | <pre>21 + input logic clk_i,<br/>22 + input logic rst_ni,</pre> |                      | Notifications                                                             | Customi |

| 6                         | •                                                               | o ···                | 义 Unsubscribe                                                             |         |

| G                         | [verible-verilog-format] reported by reviewdog                  | ····                 | You're receiving notifications becaus<br>you're watching this repository. |         |

|                           | Suggested change 3                                              |                      | 1 participant                                                             |         |

|                           | 21 - input logic clk_i,                                         |                      |                                                                           |         |

|                           | 22 - input logic rst_ni,                                        |                      | a c                                                                       |         |

|                           | 21 + input logic clk_i,                                         |                      |                                                                           | on      |

#### USING KYTHE FOR GENERATING INDEXED CODE DATABASE

- Verible can be used to perform many other tasks, e.g. generating a <u>Kythe</u> compatible indexing database

- Indexing an SV project simplifies collaboration navigate through the source code using a web browser

- <u>Showcase GitHub repository</u>

- Example index webpage

| Files                                                                                                       | 1              | // Copyright lowRISC co                           |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------|--|--|--|--|

| Files                                                                                                       | 2              | // Copyright 2018 ETH Z                           |  |  |  |  |

|                                                                                                             | 3              | // Licensed under the A                           |  |  |  |  |

| ::/                                                                                                         | 4              | // SPDX-License-Identifi                          |  |  |  |  |

| rtl/                                                                                                        | 5              |                                                   |  |  |  |  |

| ibex_alu.sv                                                                                                 | 6              | `ifdef RISCV_FORMAL                               |  |  |  |  |

| ibex_compressed_decoder                                                                                     | 7              | `define RVFI<br>`endif<br>`include "prim_assert.s |  |  |  |  |

| ibex_controller.sv                                                                                          | 8              |                                                   |  |  |  |  |

| ibex_core.sv                                                                                                | 10             |                                                   |  |  |  |  |

| ibex_cs_registers.sv                                                                                        | 11             |                                                   |  |  |  |  |

| ibex decoder.sv                                                                                             | 12             | /**                                               |  |  |  |  |

| ibex ex block.sv                                                                                            | 13             | * Top level module of                             |  |  |  |  |

| ibex fetch fifo.sv                                                                                          | 14<br>15<br>16 | */                                                |  |  |  |  |

|                                                                                                             |                | <pre>module ibex_core #(</pre>                    |  |  |  |  |

| ibex_id_stage.sv                                                                                            |                | purumotor pro                                     |  |  |  |  |

| ibex_if_stage.sv                                                                                            | 17             | parameter int unsig                               |  |  |  |  |

| ibex_load_store_unit.sv                                                                                     | 18             | parameter int unsig                               |  |  |  |  |

| ibex multdiv fast.sv                                                                                        | 19             | parameter int unsig                               |  |  |  |  |

| ibex multdiv slow.sv                                                                                        | 20             | parameter int unsig                               |  |  |  |  |

|                                                                                                             | 21             | parameter bit                                     |  |  |  |  |

| ibex_pkg.sv                                                                                                 | 22             | parameter ibex_pkg:                               |  |  |  |  |

| <ul> <li>Definitions:         <ul> <li>rtl/ibex_core.sv</li> <li>33: parameter int u</li> </ul> </li> </ul> | unsigned       | DmHaltAddr = 32'h1A110                            |  |  |  |  |

| <ul> <li>References:         <ul> <li>rtl/ibex_core.sv</li> <li>401: .DmHaltAddr</li> </ul> </li> </ul>     | ( Dm           | HaltAddr ),                                       |  |  |  |  |

#### COOPERATE WITH OTHERS: ADOPTION

- Our main focus in ongoing development was the OpenTitan project

- Currently pushing wider adoption at Google and other OT partners

- Now also used by some of the Core-V users, such as QuickLogic

- Starting collaboration with ZeroASIC

- Also working with the wider Ibex, BlackParrot, Core-V and SWeRV communities

🛟 opentitan

#### REUSE / COLLABORATE: UVM IN OPEN SOURCE

- Lots of pre-existing IP and test benches implemented in SystemVerilog

- Lots of developers familiar with UVM

- Open source UVM is necessary long term to combine commercial ecosystem with open source tools and methodologies

- Chip-making companies can benefit from open source while keeping their existing UVM codebase

- Open source tools will enable infinitely scalable, reproducible CIs

#### **OPEN SOURCE UVM**

- Ongoing work on extending Verilator with SystemVerilog features required by UVM:

- Stratified scheduler

- Randomize methods

- Class support

- One of already reached milestones is development of <u>dynamic scheduling in</u> <u>Verilator</u>

## Western Digital.

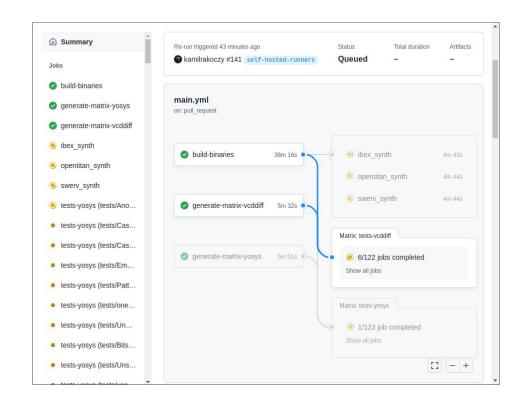

#### SCALE: GITHUB CUSTOM RUNNERS FOR CLOUD-ASSISTED CI

- Antmicro helps customers scale up ASIC development between teams and companies and into the cloud

- All the tools described here are meant to be used in a cloud context, on GitHub as well as private enterprise installations

- Mix and match open and closed components

- Use <u>custom, powerful runners</u> with scalable compute and custom peripherals e.g. FPGA boards for testing

- <u>Read more on our blog</u>

#### CUSTOM RUNNERS IN ACTION(S) WITH GITHUB

- Used for testing the UHDM integrations

- Gives us ability to do longer runs with more compute resources

- We can generate additional statistics of execution metrics, decrease resource usage and provide more insight

- Easier to find bottlenecks

#### CUSTOM RUNNERS IN ACTION - DISTANT-BES

- Run private builds, but potentially share (sanitized) build logs/results

- Upload results to own servers

- Store them for as long as needed

- Create more customized dashboards and detailed views of "what went wrong"

| e10301a9-508f-48f6-a50b                    |                        |               |    | aluation started by <b>distant</b> | on eaabf4454df6  |  |  |

|--------------------------------------------|------------------------|---------------|----|------------------------------------|------------------|--|--|

|                                            | Targets affected<br>30 | Broken Failed |    | Failed (non-critical)              | Successful<br>30 |  |  |

| TARGETS BUILD LOGS                         | INVOCATION DETAI       | LS ARTIFAC    | TS |                                    |                  |  |  |

| √ Filter                                   |                        |               |    |                                    |                  |  |  |

| 30 targets passed                          |                        |               |    |                                    |                  |  |  |

| ⊘ test (eos-s3, ubuntu, )                  | (enial counter)        |               |    |                                    | 320 seconds      |  |  |

| Ø test (eos-s3, ubuntu, bionic, counter)   |                        |               |    |                                    |                  |  |  |

| Ø test (eos-s3, ubuntu, focal, counter)    |                        |               |    |                                    |                  |  |  |

| Ø test (eos-s3, centos, 7, counter)        |                        |               |    |                                    |                  |  |  |

| ⊘ test (eos-s3, centos, 8                  | , counter)             |               |    |                                    | 362 seconds      |  |  |

| S test (eos-s3, debian, buster, counter)   |                        |               |    |                                    |                  |  |  |

| 🛇 test (eos-s3, debian, bullseye, counter) |                        |               |    |                                    |                  |  |  |

| 𝔅 test (eos-s3, debian, sid, counter)      |                        |               |    |                                    |                  |  |  |

| ⊗ test (xc7, ubuntu, xenial, counter)      |                        |               |    |                                    |                  |  |  |

| ⊗ test (xc7, ubuntu, bionic, counter)      |                        |               |    |                                    |                  |  |  |

| 𝔅 test (xc7, ubuntu, focal, counter)       |                        |               |    |                                    |                  |  |  |

| 𝔆 test (xc7, centos, 7, counter)           |                        |               |    |                                    |                  |  |  |

| ⊗ test (xc7, centos, 8, counter)           |                        |               |    |                                    |                  |  |  |

| 𝔅 test (xc7, deblan, buster, counter)      |                        |               |    |                                    |                  |  |  |

| 🕑 test (xc7, debian, bull                  | seye, counter)         |               |    |                                    | 2744 seconds     |  |  |

| 🕑 test (xc7, debian, sid,                  | counter)               |               |    |                                    | 2729 seconds     |  |  |

#### **SUMMARY**

- CHIPS Alliance is building an open source SystemVerilog tooling ecosystem - join us!

- Practical use cases are possible already now, both in local and collaborative / cloud development

- More features and use cases are actively being worked on

- We want to hear about your needs and projects!

- Join our mailing lists:

sv-wg@lists.chipsalliance.org

#### WANT TO USE OPEN SOURCE SYSTEMVERILOG TOOLS?

reach out to us: <u>contact@antmicro.com</u>